| Japanese | English |

戞侾侾夞LSI僨僓僀儞僐儞僥僗僩in壂撽俀侽侽俉

丂丂丂丂丂丂丂丂丂丂丂丂丂丂仠妛惗晹栧偺擖徿偺愝寁奣梫偵偮偄偰

桪彑丒弨桪彑偺俆僠乕儉偺愝寁偟偨俼俽俙埫崋僨僐乕僟偵偮偄偰奣梫傪偛徯夘偟傑偡丅

侾乯桪彑(揹巕忣曬捠怣妛夛俽俬俽徿) Garuda Parahyangan Team丂

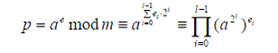

Garuda Parahyangan Team偺愝寁偺婎杮曽恓偼丄埲壓偺幃偵帵偝傟傞傛偆偵丄巜悢忲嶶墘嶼傪俀恑悢偱暘夝偟偰丄孞傝曉偟墘嶼偲偡傞婎杮揑側曽朄偵廬偭偰偄傑偡丅

偙偺幃偱偼俀庬椶偺忚梋忔嶼偑娷傑傟偰偄傑偡丅傂偲偮偼a2偱丄傕偆堦偮偼i=0偐傜l-1夞偺忚梋忔嶼偱偡丅

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

忚梋忔嶼偺堦斒宍

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

S = X x Y mod M

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

傪寁嶼偡傞応崌丄Garuda Parahyangan Team偼埲壓偺僐乕僪侾傛偆側for儖乕僾偵傛傞幚尰曽朄傪峫偊傑偟偨丅夞楬恾偱帵偡偲丄埲壓偺夞楬恾侾偑for儖乕僾偺侾夞暘偲側傝傑偡丅恾傪傒偰傢偐傞傛偆偵丄偙偺幚尰曽朄偱偼儖乕僾偺拞偵壛嶼偑懚嵼偟丄俼俽俙埫崋偺庢傝埖偆價僢僩暆偑512bit偺傛偆側戝偒側悢偵側傞応崌偵丄捠忢偺僉儍儕乕揱攄宆偺壛嶼婍偱偼壛嶼偺懍搙偑掅壓偟丄崅惈擻側夞楬傪幚尰偡傞偙偲偑偱偒傑偣傫丅丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

乮僐乕僪侾乯

丂丂丂丂丂丂丂丂丂丂丂丂丂丂 丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

乮夞楬恾侾乯

丂丂丂丂丂丂丂丂丂丂丂丂丂丂 丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

偦偙偱丄Garuda Parahyangan Team偼偙偺儖乕僾撪偺壛嶼偵張棟價僢僩悢偵墳偠偰墘嶼懍搙偑掅壓偟偵偔偄Carry Save Adder (CSA)傪梡偄偰幚憰偟傑偟偨丅

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

埲壓偺僐乕僪俀偑CSA偱偺幚憰傪帵偡傾儖僑儕僘儉偱丄for儖乕僾偺拞偺俁峴偼CSA偺儖乕僾偲側傝傑偡偑丄偙偙偱丄怴偨偵俙傪寁嶼偡傞昁梫偑惗偠丄俙偺抣傪帠慜寁嶼偟偨俿俙俛俴俤偐傜庢傝弌偡峔惉偲偟偰偄傑偡丅梫慺夞楬僽儘僢僋恾傪夞楬恾俀偵帵偟傑偡丅

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

偙偺傛偆側岺晇偵傛傝丄俆侾俀價僢僩掱搙偺戝偒側暯暘偺埫崋壔偵懳偟偰傕懳墳偱偒傞崅惈擻側夞楬傪幚尰偟傑偟偨丅壽戣偱偼丄擄堈搙傪峫椂偟偰俁俀價僢僩掱搙偺埫崋壔傪椺偲偟偰偄傑偟偨偑丄偙偺傛偆側戝偒側暯暘偺張棟傪僩儔僀偟偨偙偲偑怰嵏堳偵昡壙偝傟傑偟偨丅

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

丂丂丂丂丂丂丂丂丂丂丂丂丂丂

乮僐乕僪俀乯

乮夞楬恾俀乯