| Japanese | English |

Link

最新のLSIデザインコンテスト

・LSI デザインコンテスト 2017過去のLSIデザインコンテスト

・LSI デザインコンテスト 2016・LSI デザインコンテスト 2015

・LSI デザインコンテスト 2014

・LSI デザインコンテスト 2013

・LSI デザインコンテスト 2012

・LSI デザインコンテスト 2011

・LSI デザインコンテスト 2010

・LSI デザインコンテスト 2009

・LSI デザインコンテスト 2008

・LSI デザインコンテスト 2007

・LSI デザインコンテスト 2006

・LSI デザインコンテスト 2005

・LSI デザインコンテスト 2004

・LSI デザインコンテスト 2003

Introduction

0. はじめに

さて、今年度のLSIデザインコンテスト設計課題ですが、昨年と同様に基本に帰って基本的なエラー訂正方式である BCH符号にトライしたいと思います。BCH符号は1959および1960年にボッケンジェム(Hocquenguem)および ボーズ(Bose)と チョドーリ(Chanduri)によって発見された符号です。ガロア体と代数計算で実装できますので、初心者のデジタル回路設計 には打ってつけの課題です。学生対象のコンテストですので、小さめのデジタル回路を設計することを念頭に、符号長を 実際に使用されている長さよりかなり短くし、取り扱いやすい大きさとします。また、いくつの設計オプションを設定し、各個人 やチームによって色々な工夫ができるように、実現方法には自由度をある程度与えています。

要求されている設計内容はHDL(VHDLもしくはVerilogHDL)による設計と論理合成です。FPGA等の合成ツールでも参加できます。HDL設計に 興味のある学生はどしどし参加してください。また、余裕のある方はFPGA等で実装すれば、努力を認めて高い評価が得られると思います。 FPGA等での実装もぜひトライしてみてください。

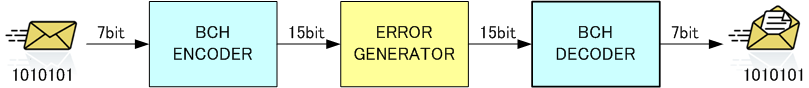

図1 送受信システム

図1に今回設計するデジタルデータの送受信システムのブロック図を示します。システムは大きく分けて、符号化器(ENCODER)と解読器(DECODER)に分かれますが、今回の設計課題は解読器(DECODER)です。実際の伝送システムを想定し、伝送途中でビットエラーが発生することを過程しています。7ビット長であるアスキーコードの送信も可能なように、7ビットの情報ビットに8ビットのパリティビットを追加し、15ビットの符号語を生成するBCH(15,7)符号とします。このBCH符号では15ビット中2ビットのランダム誤りを訂正できますので、比較的強力なエラー訂正能力をもちます。図1ではError Generationブロックがエラーを発生させます。

受信機ではこのエラーを含んだ15ビットの符号を受け取り、エラー訂正処理を行います。エラー訂正処理には有名なところではリード・ソロモン方式などがありますが、処理が複雑で学生対象のコンテストにはやや不向きです。しかしながら、このサイズのちいさなBCH符号方式では、除算回路とROMなどでエラー訂正をやることができ、回路的にはシンプルです。

今回の課題ではBCH符号の知識がなくても設計できるように、以下の仕様書で工夫をしています。設計すべきことは比較的単純ですので、デジタル設計の知識のある学生は自信を持って、課題に取り組んでください。

募集要項

- 設計仕様書

- 参加資格 : 大学・高専生による3人以下のチーム

- 必要事項を記載して以下の受付アドレスにメール送信

- レポートの提出要領については コチラ (重要)

- 最終レポート締め切り : 2010年1月29日(金)必着

EMAIL : support@LSI-contest.com

審査のポイント

- 速度、回路規模だけでなく、アーキテクチャのユニークさ、アイデア、面白さを十分考慮して審査します。

- 大学院生、学部学生、高専生のレベルに応じて審査します。

- 仕様書に従ってまじめに作るのも良いが、オモロイアイデアを歓迎します。他人と違ったことをしよう!

- 仕様の部分変更など、柔軟に受け付けます。

開催会場

- 会場名:沖縄コンベンションセンター A1会場

- 日時 :3月19日(金)13時〜17時

- 所在地:〒901-2224 沖縄県宜野湾市真志喜4-3-1

URL : http://www.oki-conven.jp/modules/tinyd3/content/index.php?id=6

実行委員長 九州工業大学情報工学部電子情報工学科 尾知 博

審査委員長 琉球大学工学部情報工学科 和田 知久

委員 九州工業大学情報工学部電子情報工学科 黒崎正行

委員 琉球大学工学部情報工学科 吉田 たけお

主催:LSIデザインコンテスト実行委員会,九州半導体イノベーション協会

共催:琉球大学工学部,九州工業大学情報工学部,特定非営利活動法人フロム沖縄推進機構,

株式会社沖縄産業振興センター,電子情報通信学会スマートインフォメディアシステム研究会,

協賛:ザイリンクス株式会社,株式会社レイドリクス,

東京エレクトロンデバイス株式会社,

サイバネットシステム株式会社,日本シノプシス合同会社,ローム株式会社,株式会社ルネサステクノロジ

後援:沖縄県,国立沖縄工業高等専門学校,CQ出版社