| Japanese | English |

Link

最新のLSIデザインコンテスト

・LSI デザインコンテスト 2016過去のLSIデザインコンテスト

・LSI デザインコンテスト 2015・LSI デザインコンテスト 2014

・LSI デザインコンテスト 2013

・LSI デザインコンテスト 2012

・LSI デザインコンテスト 2011

・LSI デザインコンテスト 2010

・LSI デザインコンテスト 2009

・LSI デザインコンテスト 2008

・LSI デザインコンテスト 2007

・LSI デザインコンテスト 2006

・LSI デザインコンテスト 2005

・LSI デザインコンテスト 2004

・LSI デザインコンテスト 2003

Introduction

審査結果

今年の審査結果を報告します

- 優勝(電子情報通信学会SIS 賞)

- チーム名 西千葉組

- 千葉大学大学院工学研究科人工システム科学専攻 M1 学生

- 千葉大学大学院 工学研究科人工システム科学専攻 修士1年

- 紀井建彦, 西辻崇, 矢澤和将

- ○デザインコンテストの要求では,16 点,64 点,128 点のFFT の実現ですが,西千葉組では実用性を 拡張し1024 点,4096 点FFT までのサポートしていました.FFT の基本動作はRADIX バタフライ回路 ですが,基本のRADIX-2 演算とRADIX-4 演算をループで繰り返し,小さいエリアで高性能な回路を実 現していました.バタフライ演算をパイプライン化するためにメモリを5 バンクとする工夫を実施し, 回路設計だけでなく,SPARTAN6 FPGA ボードに実装し,音声解析のデモを公開しました.

- 千葉大学大学院工学研究科人工システム科学専攻 M1 学生

- 準優勝(ザイリンクス賞)

- チーム名 Mozaik

- バンドン工科大学 学部学生

- Bontor Humala,Gest Ellhasya,Imran Abdurrahman

- ○インドネシア バンドン工科大学のMozaik チームは,RADIX-4 ステージ3 段とRADIX-2 ステージ1 段というオーソドックスなアーキテクチャでの設計アプローチでした.しかしながら,RADIX-4 計算を 対称性の高いSPLIT-RADIX 法を用いたり,ROM 容量の削減を試みたり,複素乗算器の回路削減を行っ たりと実用的な工夫を行い,高性能なFFT 回路を実装しました.FPGA への実装はXILINX 社の VERTEX6 を用い,MATLAB と組み合わせた画像処理のデモを行い高評価を受けていました.

- バンドン工科大学 学部学生

- 準優勝(ルネサスエレクトロニクス賞)

- チーム名 FETEL08

- University of Science, Ho Chi Minh City 学部学生

- Vietnam National University of Ho Chi Minh City 学部学生

- Duc-Phuc NGUYEN,Xuan-Vy LUU,Quoc-Minh-Dang DO

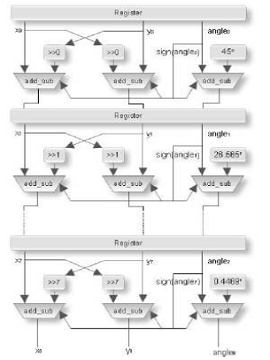

- ○彼らのFFT も3 段のRADIX-4 計算と1 段のRADIX-2 計算によるオーソドックスなアーキテクチャ でした.しかし,面白いのは通常の複素乗算器の代わりにCORDIC乗算器というものを利用しています. CORDIC 演算は複素平面の回転のような演算ですが,単純なシフトのような演算を複数段利用しての実 装で興味を引きました.以下に,彼らが使用した8 ステージCORDIC 乗算器のブロック図を示しておき ます.

- University of Science, Ho Chi Minh City 学部学生

- 準優勝(ローム賞)

- チーム名 EDA-BK

- Hanoi University of Science and Technology 学部5年生

- Nguyen Tung Lam,Nguyen Hung Cuong,Nguyen Hai Viet

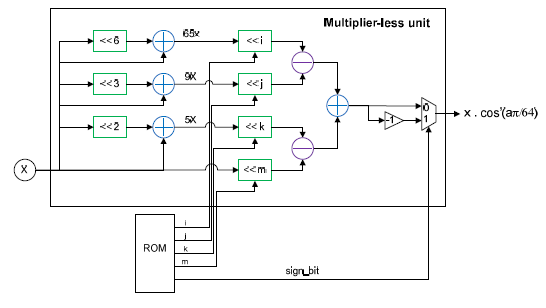

- ○ハノイ工科大学チームは,RADIX-2 を7ステージ利用するという,シンプルな構成で,必要なFFT 演算を実行するために,必要な数のステージを利用するというものです.データパス全体は符号付き18 ビットで設計され,非常にわかりやすいレポートを作成していました.TWIDDLE ファクターとの乗算 回路の削減のために,以下図に示すようなシフト等による実現を行い回路規模の削減を行っていました.

- Hanoi University of Science and Technology 学部5年生

Copyright (C) 2011 Radrix. All Rights Reserved.