第12回LSIデザインコンテスト・イン沖縄 設計仕様書 - 1

1.Small RISC Processor(SRP)アーキテクチャ

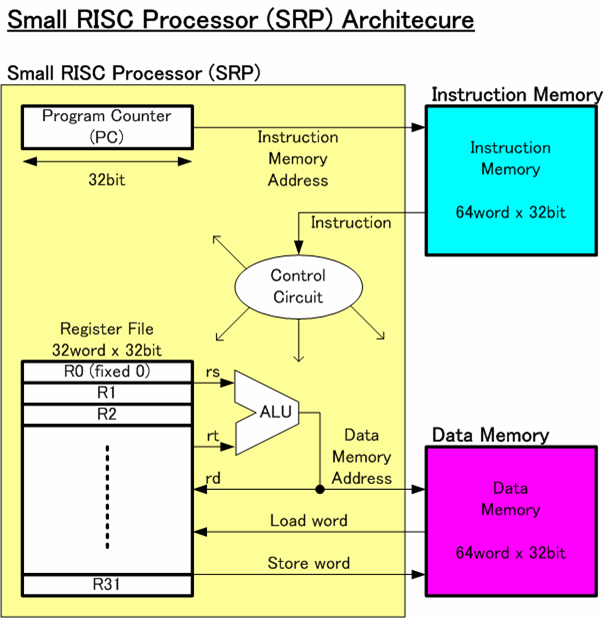

図1にSmall RISC Processor SRP アーキテクチャを示します。実は今回のSRPアキテクチャはオリジナルなものではなく、 ジョン・ヘネシーとデイビッド・パターソンの有名な図書“COMPUTER ORGANIZATION & DESIGN: the hardware / software interface”で 登場するRISCコンピュータの命令を9個に削減したものとなっています。したがって、かなり多数の方々が見たことのあるポピュラーな構成かと思います。 しかしながら、RISCマシンですので、32ワードのレジスタファイルを含んでいるものです。

図1 Small RISC Processor SRP アーキテクチャ

図1はSRP本体と、2つのメモリから構成されています。設計して頂くのはSPRです。しかし、コンピュータを動作させるには、命令とデータが必要ですので、ここでは命令を蓄える命令メモリ(Instruction Memory)、データを蓄えるデータメモリ(Data Memory)を2つの独立したメモリで構成しています。その理由は、この方がメモリの使い方が単純化され、プロセッサの設計が単純になるからです。

後ほどのプログラムの説明で、明らかになるのですが、命令メモリには32ビット(ここではワードと呼ぶ)の大きさの命令が多数蓄えられています。マイクロプロセッサこの命令メモリに蓄えられた命令をひとつずつ読み出し、その32ビット命令が示す演算を実行します。その動作を順に説明します。

①「命令フェッチ」:マイクロプロセッサにはプログラムカウンター(PC)というカウント機能があります。このPCの値は命令メモリのアドレス信号に対応しており、そのアドレスが示す場所の命令を読みだします。

②「命令デコード」:上記①で読みだされた命令の内容に従って、必要な動作をするために命令の解読を実施し、必要な制御を行います。図1ではcontrol circuitの仕事となります。

③「演算とデータメモリアクセス」:上記命令の解読結果に従って、レジスタファイルから必要な値を読みだし、ALUにて演算します。必要あれば、データメモリに対してアクセスを行い、データメモリにデータを書き込み、もしくは読み出しを行います。

④「ライトバック」:最後に、③での演算結果や、データメモリから読みだした値をレジスタファイルに書き込みます。そして、プログラムカウンター(PC)の次のサイクルの値を用意します。

上記①から④の動作でひとつの命令が実行され、繰り返すことで多数の命令を実行することができます。

「参考文献1」 refer to the section 5.1-5.3 of Morgan Kaufmann Publisher,

"COMPUTER ORGANIZATION & DESIGN: the hardware / software

interface 2nd", John L. Hennessy and David A. Patterson

「参考文献2」 日経BP社「コンピュータの構成と設計」第2版、パターソン&ヘネシー、第5.1~5.3章参照