第12回LSIデザインコンテスト・イン沖縄 設計仕様書 - 3

3.メモリアドレッシング

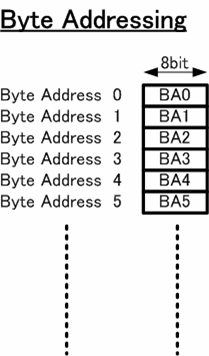

まず図2にコンピュータでは一般的であるバイト単位でのアドレッシングを示します。

図2 バイトアドレッシング

図の右の四角は8ビットの記憶ブロックを意味しており、いわゆるバイトデータに対応します。SRPではバイトアドレスを用いていますので、1バイト進むごとに、アドレス値が1上昇します。

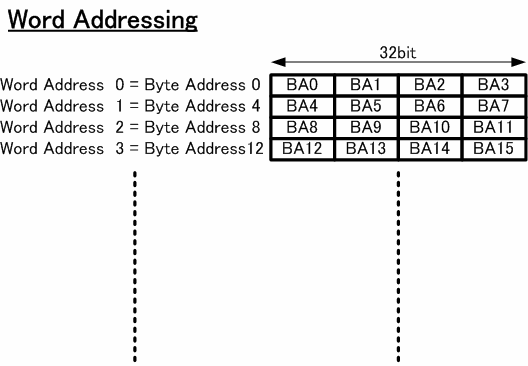

図3 ワードアドレッシング

本課題で扱う命令のサイズは4バイト(32ビット)を想定していますので、図2に示すように横方向の4つのブロックが一つの命令の記憶単位となります。したがって、命令を数えるにはワードアドレシングが便利です。このワードアドレスの値を4倍すると、4バイトブロックの左端バイトのアドレスとなります。

図1に示したSRPアーキテクチャでは2つの外部メモリがありますが、これらのメモリは32ビット単位でアドレスが振られており、メモリをアクセスする場合にはワードアドレスへの変更が必要です。

Copyright (C) 2008 Radrix. All Rights Reserved.