戞12夞LSI僨僓僀儞僐儞僥僗僩丒僀儞壂撽 愝寁巇條彂 - 8

9丏SRP徻嵶峔惉椺

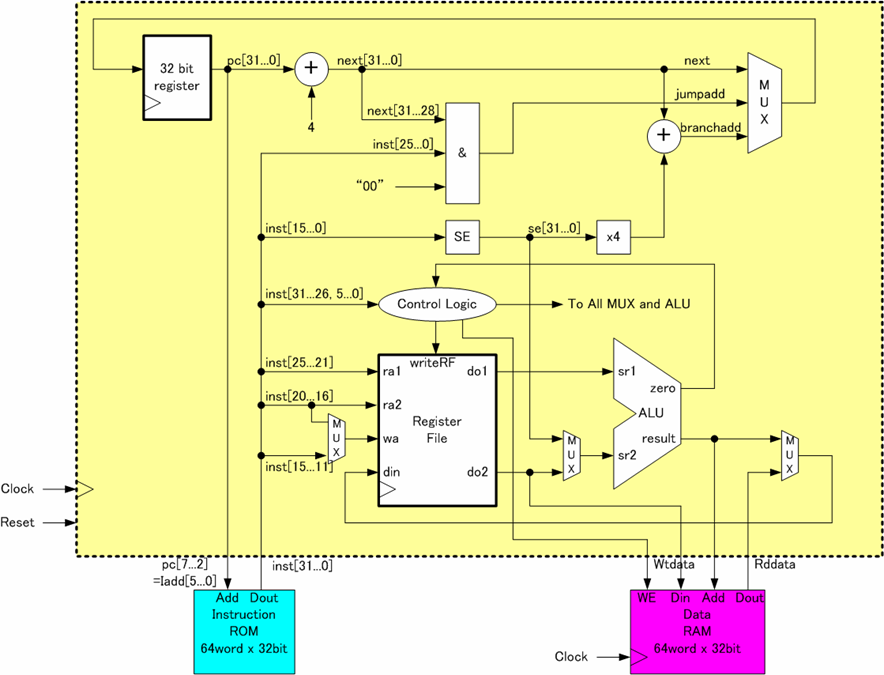

SRP偺愝寁傾乕僉僥僋僠儍偺揟宆揑側椺傪愢柧偡傞丅侾柦椷傪侾僋儘僢僋僒僀僋儖偛偲偵幚尰偡傞椺偱偁傞丅

柦椷ROM偼儚乕僪傾僪儗僗傪擖椡偝傟傞偲丄柦椷偑撉傒偩偝傟傞ROM傪憐掕偟偰偄傞丅SRP撪晹偺儗僕僗僞僼傽僀儖偱 ra1, ra2偼俀偮偺撉傒弌偟梡傾僪儗僗怣崋偱偁傝丄偙偺傾僪儗僗偵廬偭偰丄do1, do2偵儗僕僗僞偺抣偑偦傟偧傟撉傒偩偝傟傞丅 wa偼彂偒崬傒傾僪儗僗怣崋偱偁傝丄彂偒崬傓僨乕僞偼din偵梌偊傜傟傞丅writeRF=1偱丄Clock偺棫偪忋偑傝僄僢僕偱僨乕僞偑 儗僕僗僞僼傽僀儖偵彂偒崬傑傟傞丅

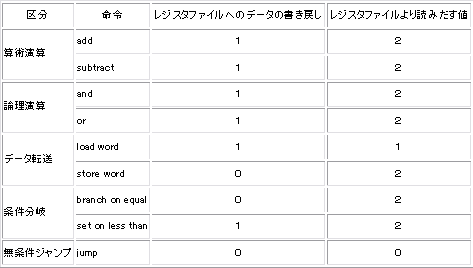

儗僕僗僞僼傽僀儖傊偺僨乕僞偺彂偒崬傒偑昁梫側柦椷偼add, sub, and, or, lw, slt偱偁傞丅昞俈偵傑偲傔傞丅

昞俈丂儗僕僗僞僼傽僀儖傊偺僨乕僞偺彂偒崬傒偑昁梫側柦椷偲撉傒弌偟僨乕僞悢

ALU偼add, sub, and, or偺墘嶼僒億乕僩偟丄偦偺墘嶼寢壥(result)偑侽偱偁傞偐偳偆偐傪挷傋傞僼儔僌(zero)傪寁嶼偡傞丅 slt柦椷偱偼丄ALU偼尭嶼傪幚峴偟丄zero僼儔僌傪挷傋傞偙偲偱丄幚憰壜擻偱偁傞丅

僨乕僞RAM傊偺彂偒崬傒偑昁梫側柦椷偼sw柦椷偱偁傝丄僨乕僞RAM偺撉傒弌偟偑昁梫側柦椷偼lw偱偁傞丅

SRP偱仮儅乕僋偼Clock擖椡傪堄枴偟偰偄傞丅僋儘僢僋偺棫偪忋傝僄僢僕偱彂偒崬傒偑敪惗偡傞弴彉夞楬偱偁傝丄 仮儅乕僋偺側偄懠偺夞楬偼偡傋偰慻崌偣夞楬偱峔惉偱偒傞丅

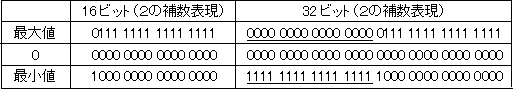

乭仌乭偼價僢僩楢寢丄乭亄乭偼壛嶼婍丄乭MUX乭偼儅儖僠僾儗僋僒丄乭SE乭偼晞崋傪曐懚偟偨價僢僩暆偺16價僢僩偐傜32價僢僩傊偺 奼挘夞楬偱偁傞丅埲壓丄昞8偵奼挘偺椺傪帵偡丅16價僢僩昞尰偱偺MSB價僢僩傪16夞嵍懁偵墑偽偣偽幚尰偱偒傞丅

昞俉丂晞崋傪曐懚偟偨價僢僩暆偺16價僢僩偐傜32價僢僩傊偺奼挘偺椺

恾俈丂SRP峔惉椺

恾俈偺塃忋偺俁擖椡MUX偼暘婒偵娭偡傞傕偺偱偁傞丅俁擖椡偺堦斣忋偑慖戰偝傟傞応崌偼捠忢偺暘婒偑側偄応崌 偱偁傝丄pc抣偼係偢偮僀儞僋儕儊儞僩偟偰偄傞丅俁擖椡偺拞墰偼柍忦審暘婒偵懳墳偟偰偄傞丅偦偺慜曽偺乬仌乭偼價僢僩偺 愙懕偱偁傝丄壓婰偵乭00乭傪楢愙偡傞偙偲偵傛傝丄係攞傪幚尰偟偰偄傞丅傑偨丄忋埵偺價僢僩偺晄懌暘係價僢僩偼傕偲偺PC偺 忋埵價僢僩傪僐僺乕偟偰偄傞丅俁擖椡偺堦斣壓偼丄忦審晅偒暘婒偑惉棫偟偨乮TAKEN乯応崌偱偁傞丅PC+4+offset*4偺寁嶼偵 側偭偰偄傞丅

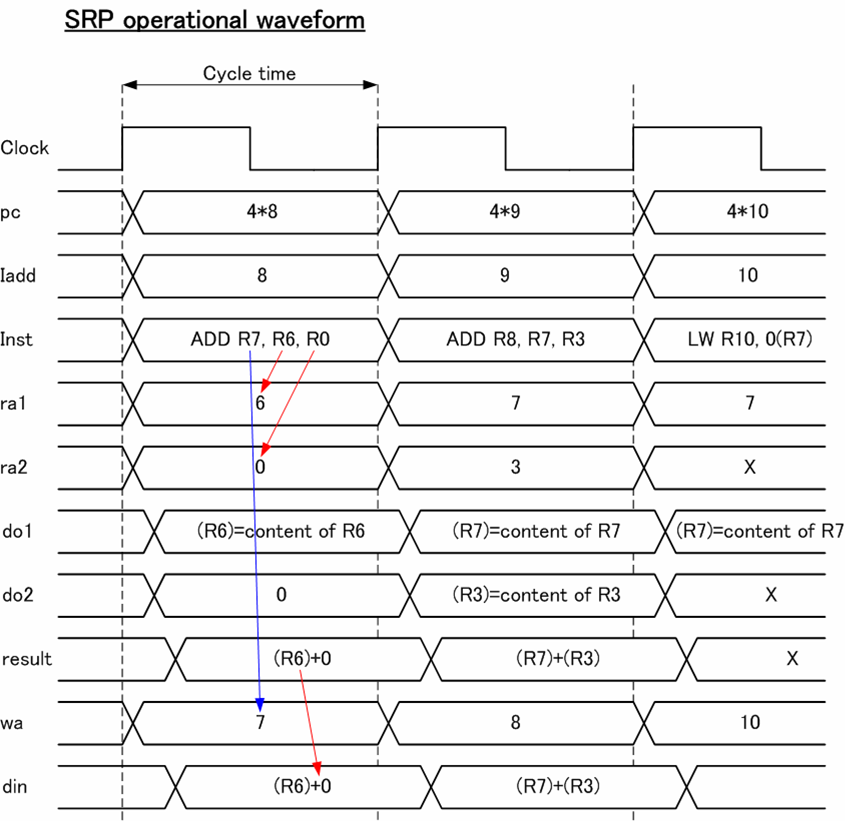

恾俉偵丄俁俀斣抧丄俁俇斣抧丄係侽斣抧傪幚峴拞偺摦嶌攇宍傪帵偡丅倫們偺抣偵傛傝丄Iadd偑惗惉偝傟丄柦椷Inst偑 柦椷ROM傛傝庢傝弌偝傟偰偄傞丅柦椷偺奺僼傿乕儖僪偺抣傛傝丄ra1, ra2, wa偑惗惉偝傟偰偄傞偙偲偑傢偐傞丅

恾俉丂SRP摦嶌攇宍恾