| Japanese | English |

Design Specification

1. Noise Cancelling Algorithm[1]1-1. Specter Subtraction Method (SS Method)

2. Implementation of the Noise Cancelling System

2-1.Separating into the Hardware and the Software

2-1-1.Features of the HW and the SW

2-1-2. Feature of Noise Cancelling System

2-1-3. Architecture

2-2. Hardware

2-2-1. Processing flow

2-2-2. Circuit structure

2-2-3. HW timing

2-3. Software

2-3-1. Source code

2-3-2. Flow chart

3. Development Environment

3-1. Hardware Design Process

3-1-1. Design Hardware Logic

3-1-2. Manual of Xilinx ISE and EDK

3-2. Software design process

4. Contest Design Target

5. SPEED and AREA

6. References

7. Download

16th LSI Design Contests・in Okinawa Design Specification - 2

2. Implementation of the Noise Cancelling System

The Noise Cancelling System should adapt in some situations and perform in real time with high quality. Various Noise Cancelling Systems are proposed today. When this system is implemented in many kinds of terminals, flexibility and real time processing are needed to adapt to changes in the environment.

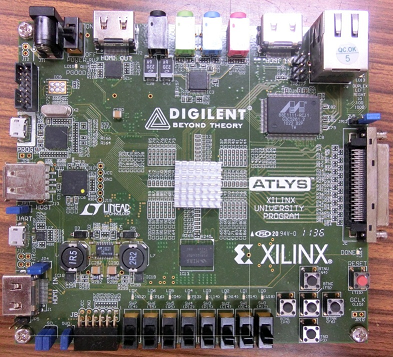

Board : ATLYS by DIGILENT co.

FPGA :Xilinx SpartanR-6 LX45 FPGA in a 324-pin BGA package

Operating frequency:100MHz

Audio :AC97 Audio Codec

Sampling frequency:48kHz

FFT Points:64

Copyright (C) 2012 Radrix. All Rights Reserved.