| Japanese | English |

設計仕様書

1. ノイズ除去アルゴリズム1-1.スペクトル・サブトラクション法

1-2.可変音声分布を利用したMAP推定法

1-2-1.MAP推定法

1-2-2.T.LotterとP.Varyの音声スペクトル分布

1-2-3.可変音声分布

2. 雑音除去システムの実装

2-1.ハード・ソフトの切り分け

2-1-1.HW・SWの特徴

2-1-2.雑音除去システムにおける処理の特徴

2-1-3.アーキテクチャ

2-2.ハードウェア

2-2-1.処理の流れ

2-2-2.回路構成

2-2-3.HWタイミング

2-3.ソフトウェア

2-3-1.ソースコード

2-3-2.フローチャート

3. 開発環境

3-1.ハードウェア設計手順

3-1-1.Hardware Logicの設計

3-1-2.Xilinx ISE 及び EDKの使い方

3-2.ソフトウェア設計手順

4. 課題

5. スピード及び回路規模の測定単位

6. 参考文献

7. ダウンロード

第17回LSIデザインコンテスト・イン沖縄 設計仕様書 - 2

2.雑音除去システムの実装

雑音除去システムは,様々な集音環境に対応し,かつ高い精度の雑音除去をリアルタイムで行うことが望まれている. 様々な雑音除去システムが提案されているが,あらゆる端末への雑音除去システムの組み込みを考えた場合, 環境の変化に対応するための柔軟性とリアルタイム性が求められる.

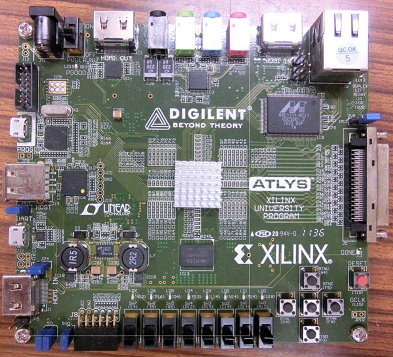

ボード:DIGILENT社製 ATLYS

FPGA:Xilinx SpartanR-6 LX45 FPGA in a 324-pin BGA package

動作周波数:100MHz

Audio :AC97 Audio Codec

サンプリング周波数:48kHz

FFT点数:64点

Copyright (C) 2013 LSI Design Contest. All Rights Reserved.