Design Specification

1.Small RISC Processor

(SRP) architecture

5.Instruction ROM and

Data Memory

BASIC

FREE

12th LSI Design Contests・in Okinawa Design Specification - 4

4.Instruction Format

According to the previous sections, you already understand

1)Instruction size is 32bits.

2)9 instructions.

3)Instruction has to indicate register address, part of memory address and jump address etc.

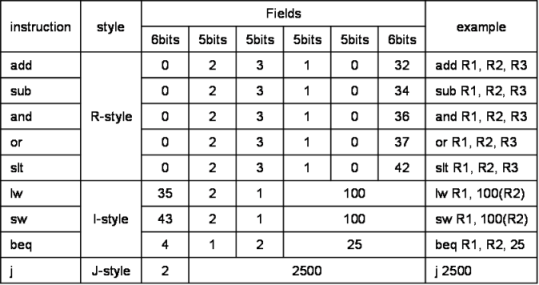

n order to indicate that information, the 32bit instruction is divided into some fields. Field is the part of bits of 32 bit instruction. Table 2 explains this instruction format. This expression of instruction is called assembler or machine word.

Table 2 Instruction format (each field’s value is shown in decimal value)

There are 3 styles in instruction format. R-style needs to indicated 3 register addresses for add, sub, and, or, slt. In order to indicate 0 to 31 register address, 5 bits fields are used. The left-most 6 bits field is “000000” in binary. This all 0 indicates R-style. The right-most 6 bits field indicated one of R-style instruction. The second right-most 5 bits field is not used.

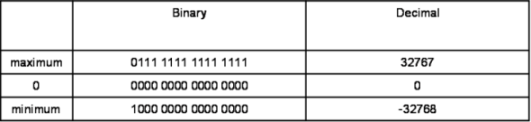

I-style can indicates two of register addresses and 16bit value. This 16 bits is two’s compliment. Then the integer indicates -32768 to +32767 in decimal. Table 3 shows the range of 16 bits. The 16 bits field is used for data memory address calculation (bytes) for lw and sw; and branch instruction offset (words).

Table 3 two’s compliment 16 bits range

Finally, J-style does not need to indicate register address. Then 26bits field is used to show absolute instruction memory address in word unit. In addition, there is not negative address then 26 bit is unsigned integer, that is, 0 or positive. If you multiply 4 with the filed, actual absolute instruction memory address (byte address) is obtained.

[Note] See example of “add R1, R2, R3” in the Table 3. Three register fields shows 2, 3, 1 from left. The order is different.

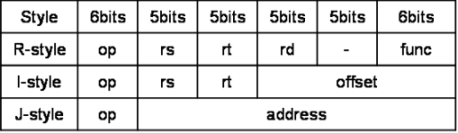

In order easily to access the fields, fields are named as shown in Table 4.

Table 4 Field Names

The op field and func field indicates operation and function. The rs and rt are source registers and rd is destination register.