| Japanese | English |

第18回LSIデザインコンテスト・イン沖縄 設計仕様書 - 6

6.課題

基本課題にて使用するvファイルをアップロードします.

Cordic vファイル:Cordic_v.zip

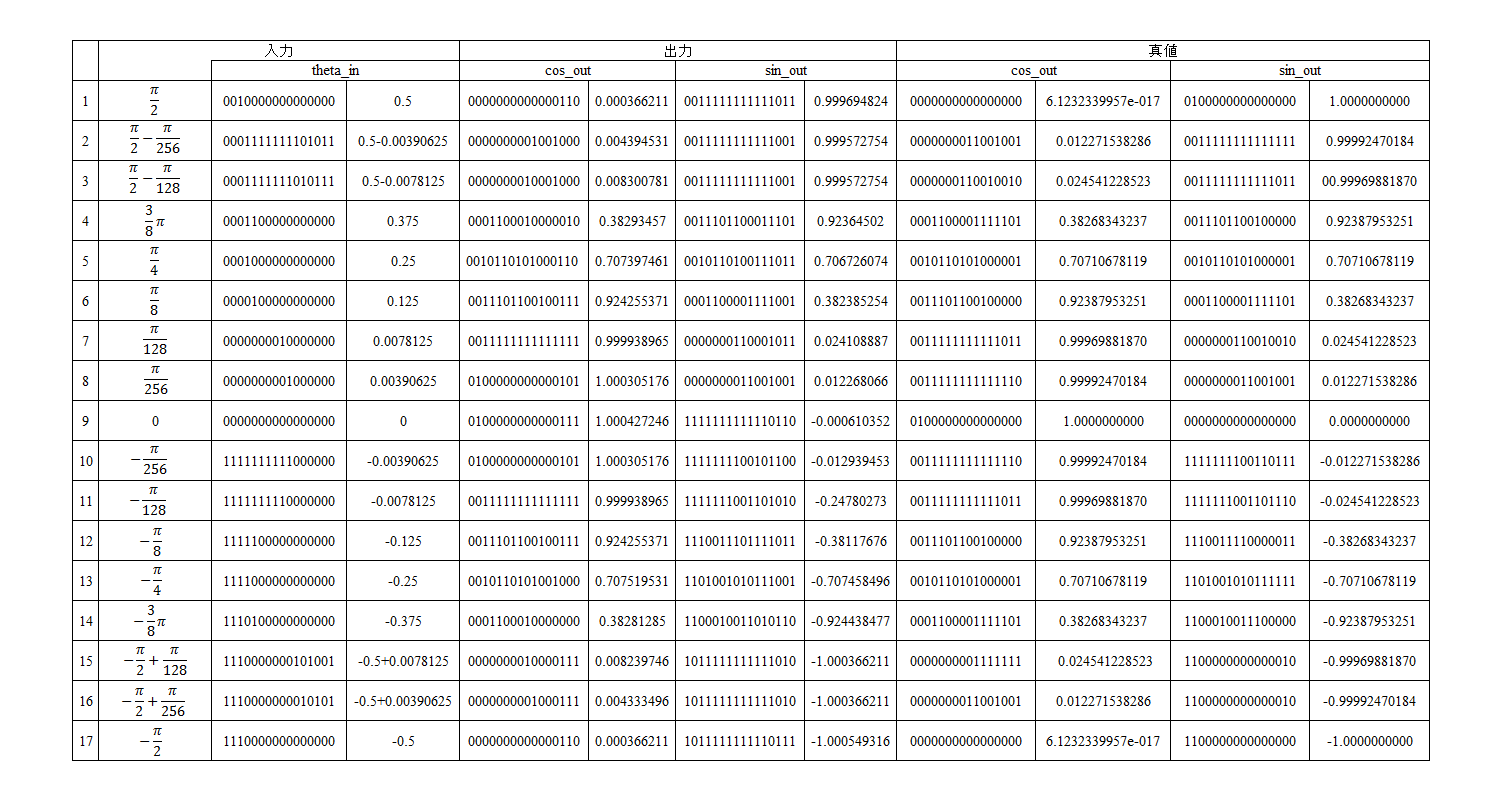

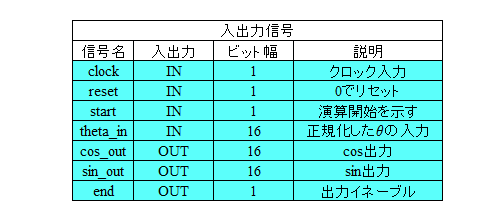

基本課題では表6-1で示すように入出力仕様を満たすCORDIC回路の設計を行ってもらいます. CORDIC回路に関してはアップロードしたvファイルを用いていただいてもいいです. もちろんvファイルを用いなくても結構です. その回路のなかのROMの値を考えて頂くという課題になります. このCORDIC回路ではthetaを入力として,\(sinθ\),\(cosθ\)を出力する回路となっています.

また,アップロードするCORDIC回路は以下のピン配置をもつこととします.

Synplify Pro もしくは Xilinx ISE® WebPACK™ を用いてestimated CLKを示してください.

クロック周波数については100MHz以上にしてください.

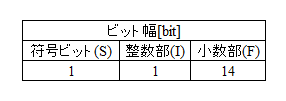

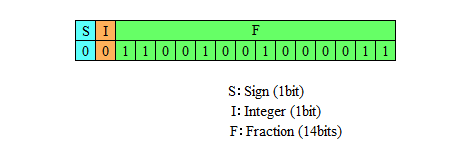

アップロードしたCORDIC回路では16bit固定小数点を用いており, その詳細を表6-3に示し,図6-1に視覚的に表示しています.

アップロードしたvファイルのCORDIC回路の入力に関して説明します. 入力に関しては3-3 アルゴリズムにてアップロードしているCプログラムの値を使用します. Cプログラムを実行すると,求めたいθの値を2進と10進で表示します. その際に得られる2進の値をCORDIC回路の入力としてください.

CORDIC回路に関して,VHDLを用いたアルゴリズム記述のソースが以下のページで公開されています.

VHDLでコードを作成している方は是非とも参考にしてください.

http://www.ie.u-ryukyu.ac.jp/~wada/vlsi14/CORDIC_ALGO.vhd

公開ソースコード 琉球大学情報工学科,和田教授

自由課題では,5章で紹介したようにいろいろなアルゴリズムを用いて三角関数回路を作成してもらいます. Level2においても表6-1の入出力仕様を満たすようにし,その際,小数点以下8bitの精度を満たすようにしてください.

余力のある方は,作成した三角関数回路を用いたアプリケーションを実装してください.

必須 小数点以下8bit精度

重視・考慮 レイテンシ,回路規模

その他自分たちの回路がアピールできるような評価,および動作ビデオなど

小数点以下8bit精度を満足していれば,Level2の課題として評価します