第13回LSIデザインコンテスト・イン沖縄 設計仕様書 - 3

3.符号化器(ENCODER)の回路構成と動作説明

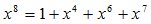

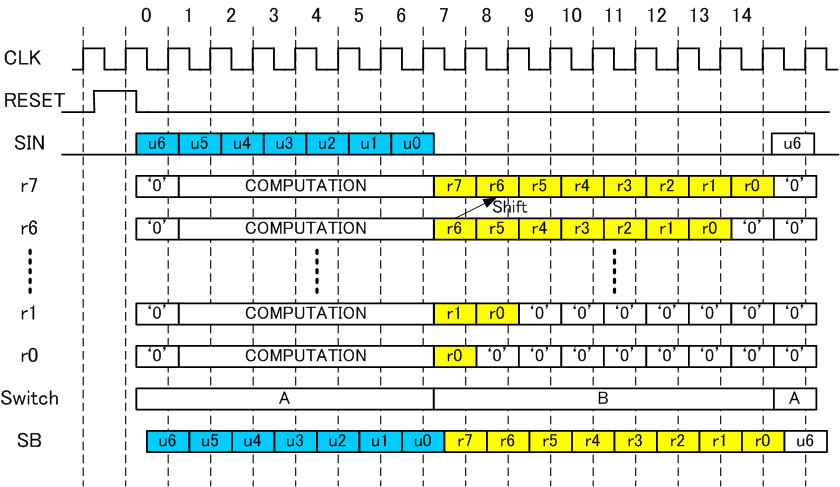

図2に送信機の回路図を示します。クロックに同期して、SIN入力より情報ビットを u6, u5, ..., u0の順に入力します。このとき2つのスイッチはA側に接続しておきます。そうすると、SB出力端子よりu6, u5, ..., u0がそのまま出力されると同時にr7, r6, ..., r0フリップフロップと排他的論理輪EXORで構成されるガロア体の割り算の余り計算回路で(3)式で示される係数が計算されます。

… (5)

… (5)

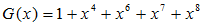

で割り算を行いますので、

… (6)

… (6)

なる式を用いて式の次数を下げることになります。すなわち、SINからの信号は8次の係数に対応し、8次の係数が1の場合、0次、4次、6次、7次の係数に’1’をEXORとることになります。回路をみるとまさに(6)式で示す計算をやっていることになります。結果的に、INに7個の値をすべて入力すると、r7, r6, ..., r0なるフリップフロップにガロア体の割り算の余りの係数が発生します。

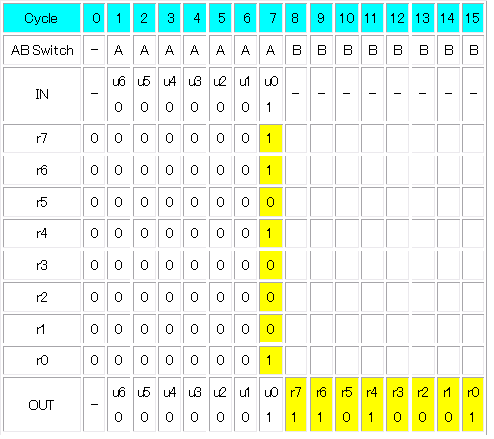

その後にスイッチをB方向に接続すると、r7, r6, ..., r0なる係数は右方向へ順にシフトし、OUT端子から出力されます。この詳しい動作タイミングを図3に示します。

図2 送信機の回路図

図3 送信機の動作波形図

図3ではRESET信号を用い、RESET信号によりr7, r6, ..., r0なるフリップフロップの同期リセットも行っています。

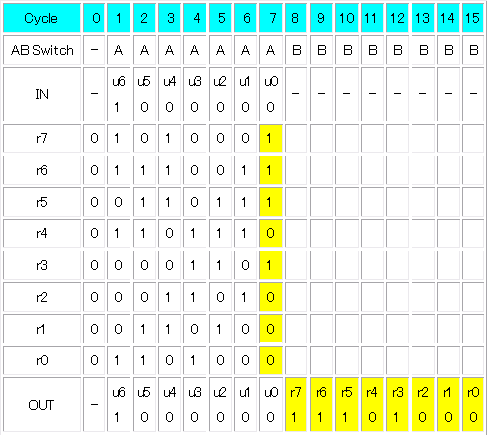

表3および表4に情報ビットが(0,0,0,0,0,0,1) の場合と、(1,0,0,0,0,0,0) の場合のレジスタの値の時間的変化を示しておきます。

情報ビットが(0,0,0,0,0,0,1) の場合は、u0=1すなわち、8次の係数が1であり、

… (6)

… (6)

すなわち、r7=r6=r4=r0=1なる処理を1回やっていることが理解できると思います。

表3 情報ビット=(0,0,0,0,0,0,1)を送信する場合の送信回路の動作

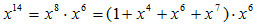

情報ビットが(1,0,0,0,0,0,0)の場合は、u6=1すなわち、14次の係数が1であり、

… (6)

… (6)

なる処理をサイクル1で行うことで、その後の6サイクルでシフト動作を行うことで等価的に、

… (8)

… (8)

やっていることが理解できると思います。

以下に動作を説明しますので、これを丁寧に理解することで、ENCODE方法を理解することができると思います。

Cycle=1 では、u6=1が入力され、r7=r6=r4=r0=1なる処理を行います。

Cycle=2では、まずシフト動作によりr7=r5=r1をたてようし、u5=0とシフトであふれたr7=1のexor=1により、r7= r6= r4= r0に1を立てようとしますが、この両者のexorにより結果的にはr7=0, r6=r5=r4=1, r3=r2=0, r1=r0=1という状態になります。

Cycle=2からCycle=3への変化時には、u4=0でかつ以前のr7=0であったので、exor=0となり、ここではシフト動作のみが発生します。

表4 情報ビット=(1,0,0,0,0,0,0) を送信する場合の送信回路の動作