戞13夞LSI僨僓僀儞僐儞僥僗僩丒僀儞壂撽 愝寁巇條彂 - 6

6. 僔僗僥儉峔惉

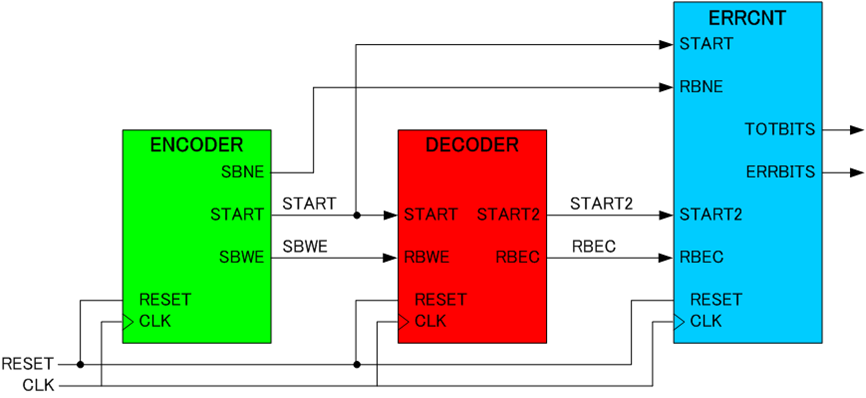

崱夞愝寁偡傞僔僗僥儉偺峔惉傪恾俉偵帵偟傑偡丅僔僗僥儉偼戝偒偔傢偗偰丄ENCODER偲DECODER丄偦偟偰庴怣婡偱僄儔乕掶惓偝傟偨庴怣婡偺弌椡乮RBEC乯偺僄儔乕偺悢傪僇僂儞僩偡傞偨傔偺ERRCNT乮僄儔乕僇僂儞僩婡乯偐傜側傝丄愝寁偟偰傕傜偆偺偼丄DECODER偲ERRCNT偱偡丅幚嵺偵夞楬崌惉傪峴偄丄夞楬婯柾傗僗僺乕僪傪媮傔傞偺偼RECEIVER偩偗偲側傝丄ERRCNT偼帺暘偱愝寁偟偨RECEIVER偺僄儔乕掶惓偺擻椡偺昡壙偵巊梡偟傑偡丅

恾8 僔僗僥儉峔惉恾

(ENCODER偺愢柧)

ENCODER偼憲怣懁偱偁傝丄7價僢僩偺忣曬價僢僩楍U(x)傪惗惉偟丄8價僢僩偺僄儔乕掶惓梡價僢僩楍R(x)傪晅壛偟偰丄15價僢僩偺憲怣僨乕僞SB(倶乯傪惗惉偟傑偡丅

偝傜偵ENCODER偼揔摉側僄儔乕傪敪惗偝偣丄偦偺弌椡傪SBWE(Send Bit With Error)抂巕偵弌椡偟傑偡丅SBWE偵偼楢懕揑偵侾偐侽偺怣崋偑僋儘僢僋CLK偵摨婜偟偰弌椡偝傟傑偡丅偙偺15價僢僩偺憲怣偼楢懕揑偵敪惗偟丄忢偵15僒僀僋儖偛偲偵7價僢僩偺忣曬價僢僩楍偲8價僢僩偺僄儔乕掶惓梡價僢僩楍偑憲怣偝傟傑偡丅

START怣崋偼15僒僀僋儖拞1僒僀僋儖婜娫偺傒丄侾傪弌椡偟丄15價僢僩偺憲怣僨乕僞偺愭摢埵抲傪帵偟傑偡丅

SB偼RECEIVER偵傛傞僄儔乕掶惓偑偆傑偔偱偒偰偄傞偐傪挷傋傞栚揑偵梡堄偝傟偨怣崋偱偁傝丄SBWE抂巕偺弌椡偵懳墳偟偨僄儔乕偑娷傑傟偰側偄惓偟偄怣崋傪弌椡偟傑偡丅幚嵺偺捠怣僔僗僥儉偱偼偙偺傛偆側怣崋偼偁傝傑偣傫偑丄偙偙偱偼僄儔乕掶惓偺昡壙偺偨傔偵摿暿偵梡堄偟傑偡丅

(DECODER偺愢柧)

DECODER偼庴怣懁偱偁傝丄僋儘僢僋偵摨婜偟偰丄ENCODER偐傜偺憲怣怣崋SBWE傪庴偗庢傝傑偡丅15僒僀僋儖偛偲偵僄儔乕掶惓傪峴偄丄僄儔乕掶惓偝傟偨15價僢僩傪RBEC抂巕偵弌椡偟傑偡丅偙偺弌椡偺15價僢僩偵偼僄儔乕掶惓梡價僢僩傕娷傑傟傑偡偑丄偡傋偰偺僄儔乕掶惓傪峴偄弌椡偟傑偡丅傑偨丄RBEC偺愭摢埵抲傪帵偡偨傔偵丄START2怣崋傪梡偄傑偡丅偙傟偼START怣崋傪DECODER撪偱偺僄儔乕掶惓偺儗僀僥儞僔乕抶墑偝偣偨怣崋偱偡丅

乮ERRCNT丗僄儔乕僇僂儞僩婡乯

ERRCNT偼庴怣婡偺昡壙梡偺僽儘僢僋偱偁傝丄夞楬崌惉摍偼峴偄傑偣傫丅ENCODER傛傝START怣崋偲僄儔乕偺側偄憲怣怣崋SB傪庴偗庢傝傑偡丅偟偨偑偭偰丄偄偮傕惓偟偄忣曬價僢僩傪抦傞偙偲偑偱偒傑偡丅傑偨丄ERRCNT偼DECODER傛傝僄儔乕掶惓偝傟偨忣曬價僢僩傪RBEC抂巕傛傝庴偗庢傝傑偡丅ERRCNT偼惓偟偄忣曬價僢僩偲僄儔乕掶惓偝傟偨忣曬價僢僩傪斾妑傪峴偄丄撪晹偵帩偮揔摉側戝偒偝偺儗僕僗僞偵椵愊偺僄儔乕偺敪惗夞悢傪婰壇偟丄奜晹傊ERRBITS抂巕傪捠偟偰弌椡偟傑偡丅摨帪偵丄椵愊偺僩乕僞儖庴怣價僢僩悢傪奜晹傊TOTBITS抂巕傪捠偟偰弌椡偟傑偡丅偟偨偑偭偰丄ERRBITS/TOTBITS傪寁嶼偡傟偽價僢僩僄儔乕棪傪抦傞偙偲偑偱偒傑偡丅

DECODER偼僄儔乕掶惓弌椡傪弌偡傑偱偺儗僀僥儞僔乕乮抶墑乯偑偁傝傑偡偺偱丄ERRCNT偼偦偺抶墑傪峫椂偟偰僄儔乕悢傪僇僂儞僩偡傞傛偆偵愝寁偟偰偔偩偝偄丅

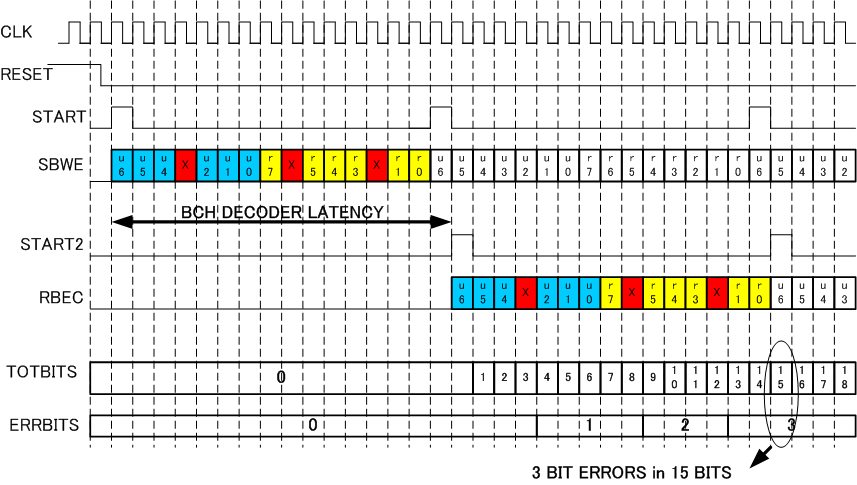

7. 摦嶌僞僀儈儞僌椺

恾9 僔僗僥儉摦嶌僞僀儈儞僌椺

恾俋偵摦嶌僞僀儈儞僌偺椺傪帵偟傑偡丅RESET怣崋偺夝彍偺屻丄ENCODER偼SBWE乮Sen倲 Bits With Error乯怣崋丄SB乮Sen倲 Bits without error乯怣崋丄START怣崋傪弌椡偟傑偡丅15僒僀僋儖偑傂偲偮偺扨埵偲側偭偰偍傝丄嵟弶偺7僒僀僋儖偱忣曬價僢僩偑丄偦偺屻偺8僒僀僋儖偱僄儔乕掶惓梡價僢僩偑憲怣偝傟傑偡丅SBWE偼僄儔乕晅偺怣崋偱偁傝丄偁傞妋棪偱僄儔乕偑敪惗偟傑偡丅徻偟偔偼梌偊傜傟偨ENCODER偺VHDL婰弎傪尒偰偔偩偝偄丅

DECODER偼SBWE怣崋傪庴怣偟丄僄儔乕掶惓傪峴偄丄RBEC乮Received Bits Error Corrected乯偵僄儔乕掶惓傪偟偨忣曬價僢僩傪弌椡偟傑偡丅僄儔乕掶惓梡價僢僩傕僄儔乕掶惓張棟傪峴偄丄ERRCNT偱寁應偱偒傞傛偆偵偟傑偡丅

ERRCNT偼15價僢僩偺忣曬價僢僩偍傛傏僷儕僥傿價僢僩偵懳偡傞僄儔乕偺椵愊抣偲張棟偟偨僩乕僞儖價僢僩悢傪帵偡傕偺偱偡丅