| Japanese | English |

設計仕様書

1. ノイズ除去アルゴリズム[1]1-1.スペクトル・サブトラクション法

2. 雑音除去システムの実装

2-1.ハード・ソフトの切り分け

2-1-1.HW・SWの特徴

2-1-2.雑音除去システムにおける処理の特徴

2-1-3.アーキテクチャ

2-2.ハードウェア

2-2-1.処理の流れ

2-2-2.回路構成

2-2-3.HWタイミング

2-3.ソフトウェア

2-3-1.ソースコード

2-3-2.フローチャート

3. 開発環境

3-1.ハードウェア設計手順

3-1-1.Hardware Logicの設計

3-1-2.Xilinx ISE 及び EDKの使い方

3-2.ソフトウェア設計手順

4. 課題

5. スピード及び回路規模の測定単位

6. 参考文献

7. ダウンロード

第16回LSIデザインコンテスト・イン沖縄 設計仕様書 - 2-1

2-1. ハード・ソフトの切り分け

2-1-1. HW・SWの特徴

あるアルゴリズムで構成されたシステムの実装方法において,ソフトウェアの特徴は, 様々な演算がソースコードの書き換えのみで実現できることである. また,ソフトウェアではCPU内に用意された回路をループすることで演算をおこなうため,回路規模は変わらないが, 演算速度は遅くなるという特徴がある.一方,ハードウェアの利点は,演算速度が早いことがあげられる. しかし,処理ごとに回路が増えるため回路規模は大きくなるという欠点がある.

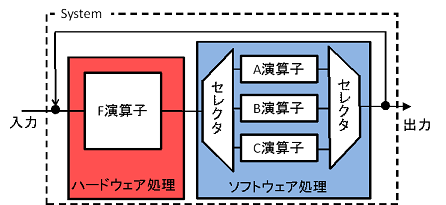

例として下図に示すようなシステムを考える.このシステムでは,F演算子の結果から分岐し,A,B,Cのいずれかの演算が行われるものとする. この時,必ず計算される演算を固定演算とし,必ず演算されるとは限らない演算を変動演算と定義する. 固定演算子の場合,演算速度の速いハードウェア処理が望ましい.一方,変動演算子の場合,ハードウェア処理をすると 演算していない回路が存在することになり,回路規模の観点から,非効率である.よって,固定演算子はハードウェアで, 変動演算子はソフトウェアで処理することが適切である.

2-1-2. 雑音除去システムにおける処理の特徴

周波数領域での雑音除去を考えた場合,処理の流れは次のようになる.

雑音除去のためのアルゴリズムはスペクトルゲインの推定方法によって様々であるが,これは周波数領域のみでの処理である. よって時間領域での処理は常に変わらない.以上のことから,時間領域での処理は固定演算,周波数領域での処理は変動演算であるといえる.

2-1-3. アーキテクチャ

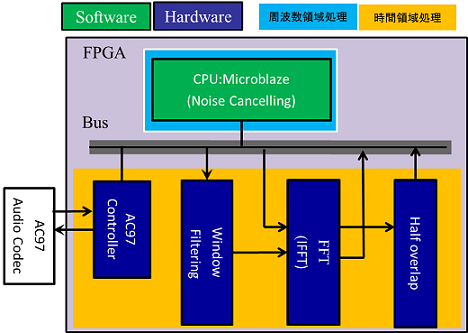

時間領域での処理は固定演算であることからHW処理で行い,周波数領域での処理は変動演算であるのでSW処理を行う. 開発する雑音除去システムのアーキテクチャを下図に示す.回路規模を小さくするため,FFT演算器でIFFTを行う回路構成になっている.

1.AC97 Audio Codecで音声信号(時間領域信号)をAD変換し,AC97 Controllerを介してCPUに取り込む.

2.CPUから窓関数をかける回路に音声信号を出力する.

3.窓関数をかけた後,FFTを行い,周波数信号に変換し,CPUに再び取り込む.

4.CPU内で雑音除去(SW処理)を行う.

5.CPUからFFT回路(IFFTを行う)に出力し,周波数領域信号から時間領域信号に変換する.

6.IFFT後,時間領域信号にHalf Overlapを行い,CPUに出力する.

7.CPUはAC97 Controller を介して AC97 Audio Codecに音声信号を出力し,DA変換が行われる.