| Japanese | English |

設計仕様書

1. ノイズ除去アルゴリズム[1]1-1.スペクトル・サブトラクション法

2. 雑音除去システムの実装

2-1.ハード・ソフトの切り分け

2-1-1.HW・SWの特徴

2-1-2.雑音除去システムにおける処理の特徴

2-1-3.アーキテクチャ

2-2.ハードウェア

2-2-1.処理の流れ

2-2-2.回路構成

2-2-3.HWタイミング

2-3.ソフトウェア

2-3-1.ソースコード

2-3-2.フローチャート

3. 開発環境

3-1.ハードウェア設計手順

3-1-1.Hardware Logicの設計

3-1-2.Xilinx ISE 及び EDKの使い方

3-2.ソフトウェア設計手順

4. 課題

5. スピード及び回路規模の測定単位

6. 参考文献

7. ダウンロード

第16回LSIデザインコンテスト・イン沖縄 設計仕様書 - 2-2

2-2. ハードウェア

ここではハードウェアでの処理の流れを説明する.次章(2-3.ソフトウェア)と併せて見ていただければ,より理解しやすくなります.

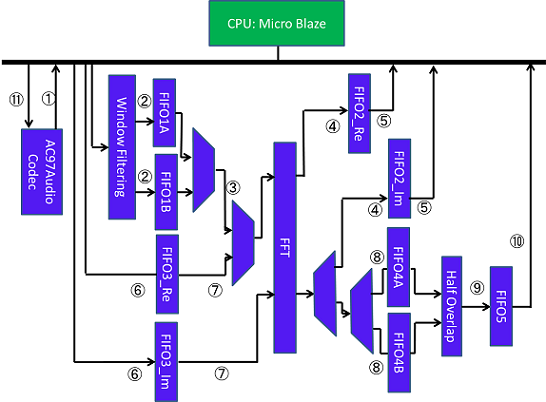

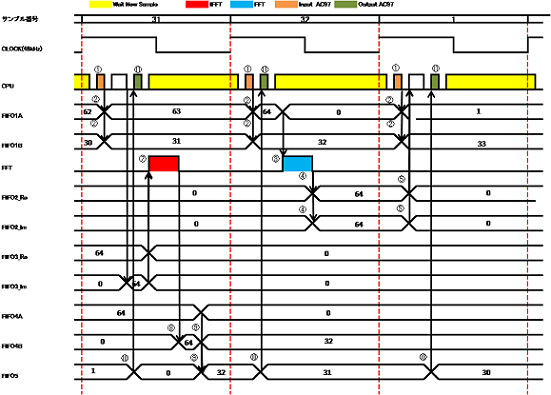

2-2-1. 処理の流れ

1. CPUにAC97からサンプルデータを取り込む.

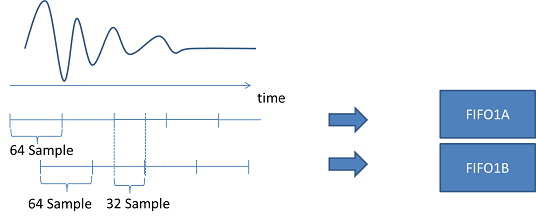

2. 取り込んだサンプルデータをCPUからWindow Filteringに1サンプルデータごとに出力する.64サンプルごとに

切り出しFIFO1AとFIFO1Bに格納する.この時,下図のようにFIFO1AはFIFO1Bより32サンプルデータ分早く格

納される.

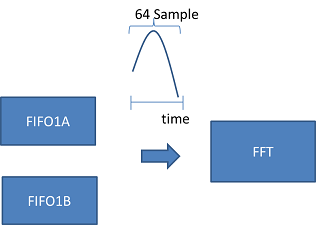

3. FIFO1A又はFIFO1Bに64個サンプルデータが格納されたら,FFT回路に出力する.

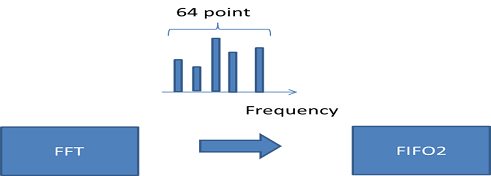

4. FFT後FIFO2に格納する(FFTした結果の実数部をFIFO2_Reに虚数部をFIFO2_Imに格納する).

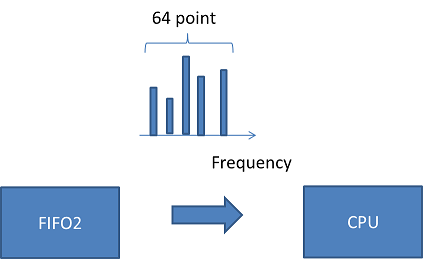

5. CPUにFIFO2からデータを取り込む.

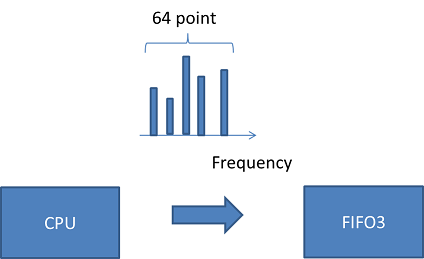

6. CPUからFIFO3へデータを出力する(FFT回路の実数部に入力するデータをFIFO3_Reに虚数部に入力するデ

ータをFIFO3_Imに格納する).

7. FIFO3に64point分のデータが溜まったらFFT回路に出力して,IFFTを行う.

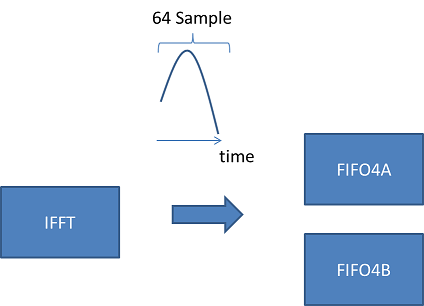

8. IFFTした結果をFIFO4A又はFIFO4Bに格納する.FIFO1Aに格納されていたデータはFIFO4Aに格納し,FIFO1B に格納されていたデータはFIFO4Bに格納する.

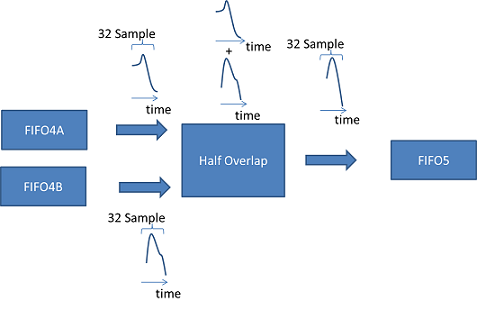

9. FIFO4A又はFIFO4Bに64個のサンプルデータが溜まったとき,もう片方には32個のサンプルデータが溜まっ

ている.FIFO4AとFIFO4Bから32個のサンプルデータを取り出し,Half Overlapを行い,FIFO5に格納する.

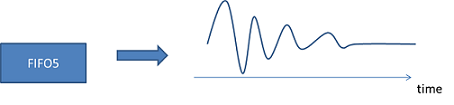

10. CPUにFIFO5からサンプルデータを取り込む.

11. CPUからAC97にサンプルデータを出力する.