| Japanese | English |

14th LSI Design Contests・in Okinawa Design Specification - 1

1. SYSTEM OVERVIEW

The amount of information of picture on digital form is quite large compared with commonly available bandwidth to transmit them over the internet or wireless communication. Another application like video requires thousand of pictures, which need a lot of space for storing them. Therefore, we need a way for reducing the storage requirement for image data. One of the common method is the image compression.

The image compression system is able to reduce image data size without significantly reducing image quality. It removes the least information on the image which considered as high frequency. The human eye is more difficult to see the difference in high frequency than low frequency. Moreover, most of digital image is low frequency. By eliminating the higher frequency we can significantly reduce the image data size. This elimination is considered as lossy compression technique. It means that the compressed image is not exactly same as the original image.

The objective of this contest is to design the image compression and decompression system using HDL (VHDL or Verilog HDL) and to synthesize digital circuits using Synopsys design analyzer or any other EDA tools. Making FPGA is also optional but our judges love to see your FPGA designs.

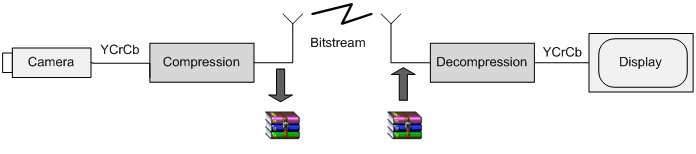

Figure 1 shows the block diagram of proposed image compression system. An object is captured by a camera in YCrCb format (Y: luminance, Cb: Chrominance-Blue, and Cr: Chrominance-Red). The Compression Module will compress the image into bitstream data. The compressed bitstream data will be ready to be transmitted or stored.

At the receiver side, the birstream data will be decompressed into original image by the Decompression Module. The decompressed image is in YCrCb format, and ready to be displayed in Monitor.

図1 画像圧縮システム