| Japanese | English |

第14回LSIデザインコンテスト・イン沖縄 設計仕様書 - 4

4. 2D-DCT ハードウェアアーキテクチャ

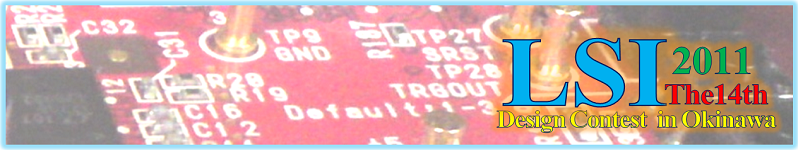

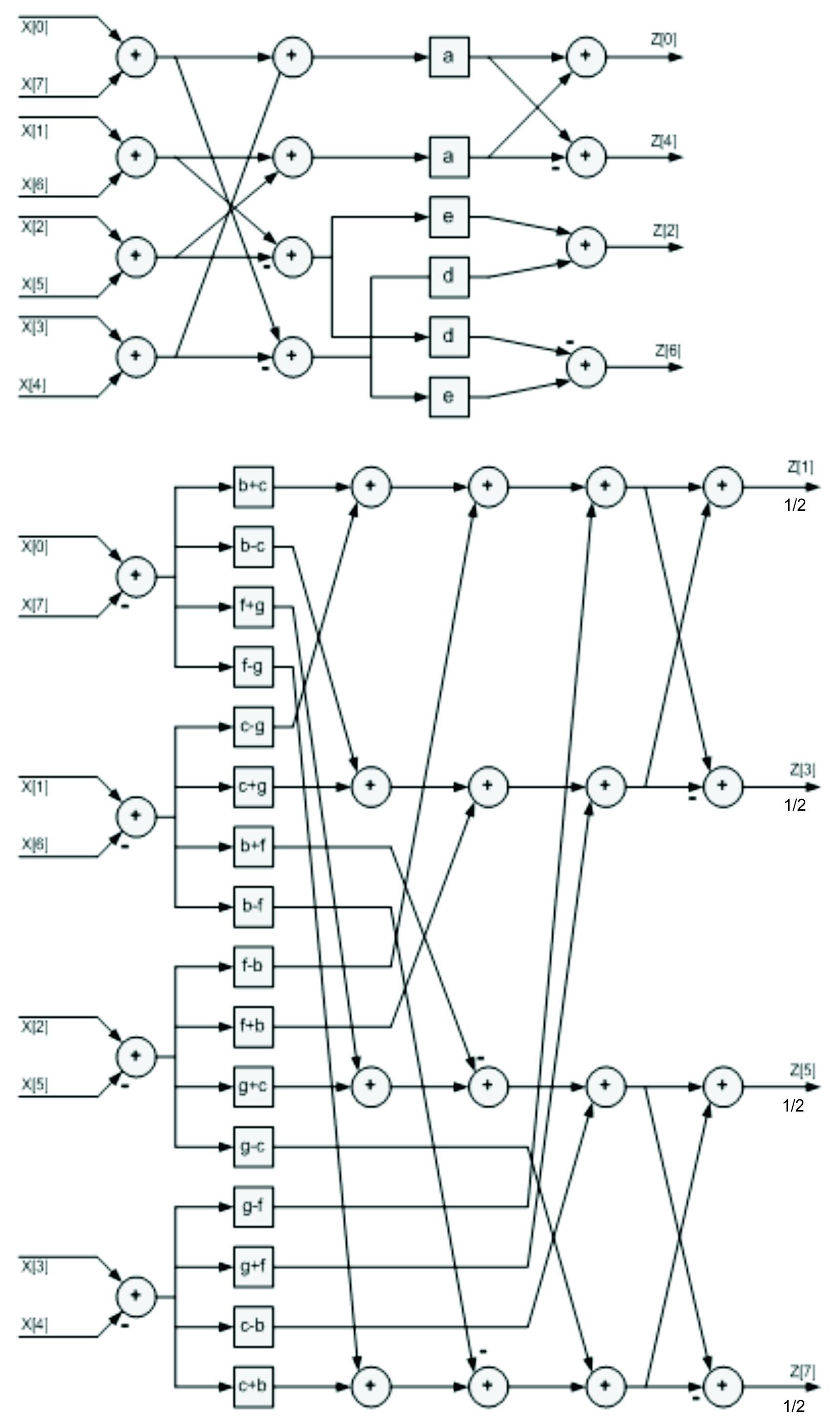

本章では例として1D-DCTアーキテクチャを説明します。式(5)より、アーキテクチャは以下の図5のように表すことができます。ここで図中の四角形は乗算器、円は加算器を表しています。また四角形中のアルファベットは式(5)で示した係数で定義されており、これらの係数によって乗算されます。

もしあなたがたのチームで別の手法もしくは別のアーキテクチャを提案できるのであれば、そちらを実装してみてください。乗算器および加算器の数を減らすことで、ハードウェア実装の最適化を行わなければなりません。多くの回路規模と電力を節約するために、乗算器および加算器の数はできるだけ少なくなるように設計してください。そして効率的な回路にするために、演算効率の良い乗算器を実装すべきです。

図5 1D-DCTアーキテクチャ

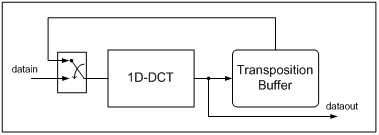

2D-DCTアーキテクチャを以下の図6に示します。最初の1D-DCTは行ごとに行列を受信します。転置バッファは1D-DCTの演算結果を行毎に受信し、転置した上で列ごとに二番目の1D-DCTに入力します。

図6 2D-DCTアーキテクチャ

Copyright (C) 2010 Radrix. All Rights Reserved.