| Japanese | English |

第15回LSIデザインコンテスト・イン沖縄 設計仕様書 - 4-2-1

4-2-1. N=4 のFFT回路

(1) 回路設計

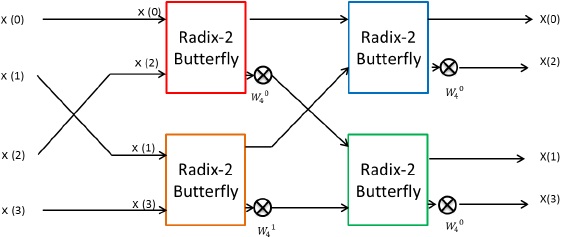

A-1章にてパラレル入力に対する4点FFT回路設計を設計した。

パラレル入力に対するFFT回路は設計が容易であり入力に対して出力が行われるまでのLatencyが0などの利点もあるが、回路規模が膨大になるという欠点もある。

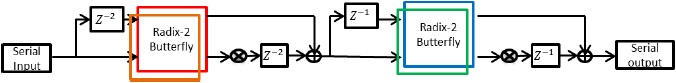

設計の際に遅延を行うDelayブロックやマルチプレクサを表すMUXブロックを用いて,バタフライ演算回路を複数回使うことでのバタフライ演算回路数を減らすことができれば、回路規模を縮小できる。

この章では、シリアル入力に対して4点FFTを行う回路を設計する。

概念的ブロック図を以下に示す.

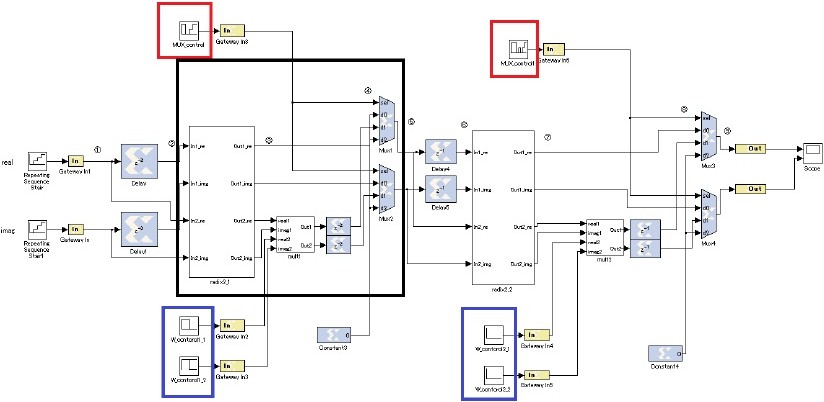

図19の赤枠、青枠のシーケンスをそれぞれ説明する。

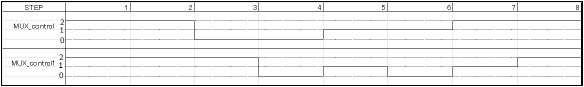

a) MUX_control

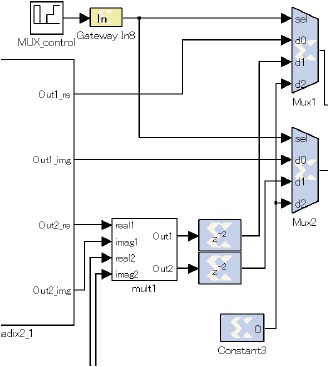

図19の黒枠内を拡大して図20に示す。

図19のマルチプレクサMUX1、MUX2はsel(セレクタ)=0~2のとき、d0~d2の値をそれぞれ出力する. 赤枠のMUX_controlというブロックはマルチプレクサのセレクタに入力する信号を制御するシーケンスであり、これによりマルチプレクサの出力信号を決定している。

パラメータを図21に示す。

図16から読み取れるようにMUX_controlから出力される値はステップごとに変化している。 これによりバタフライ演算回路の出力信号のうちFFTに必要な信号のみ次のバタフライ演算回路へ送るよう制御を行っている。

b) W_control

青枠のW_controlは回転因子Wを表すシーケンスである。

STEPごとに複素乗算する回転因子の値(実部、虚部)を変化させて、バタフライ演算を行う。

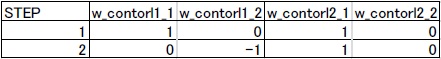

シーケンスのパラメータを表5に示す。

表5: W_controlシーケンスのパラメータ

表5からわかるように、図18のMULT1において最初のステップでは

![]() を乗算し、次のステップでは

を乗算し、次のステップでは

![]() を乗算している。

MULT2においては常に

を乗算している。

MULT2においては常に ![]() を乗算している。

を乗算している。

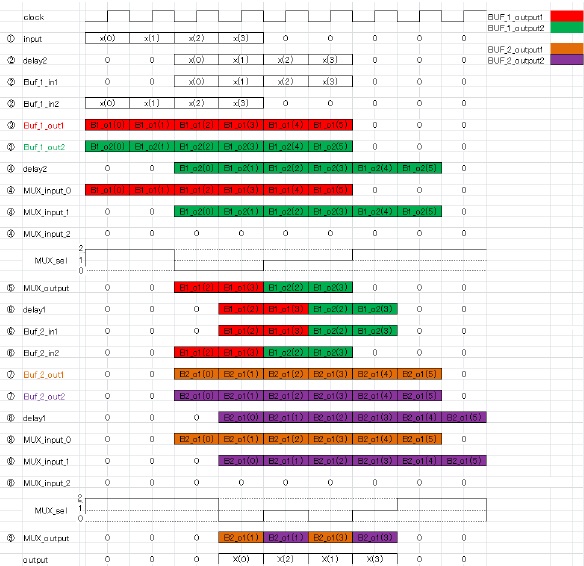

図18のシリアル入力に対する4点FFT回路のタイミングチャートを図22に示す。

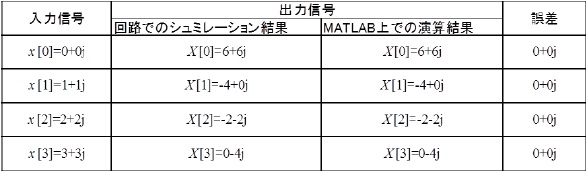

(2) 検証

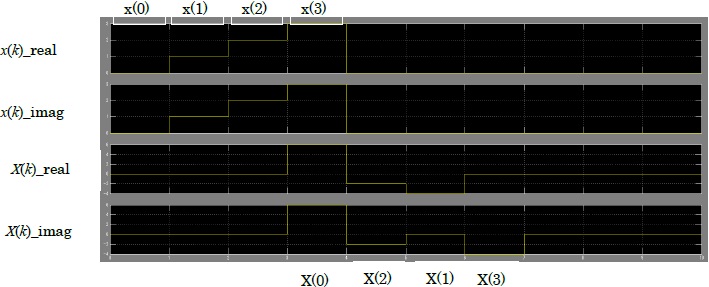

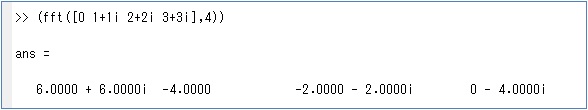

入力信号を x(0)=0+0j, x (1)=1+1j, x(2)=2+2j, x(3)=3+3j として回路のシミュレーションを行った。 出力波形を図23に示す。

図23において,出力信号は X(0)=6+6i, X(1)=-4+0i, X(2)=-2-2i, X(3)=0-4i となり、MATLABの演算結果(図23参照)と一致していることが確認できる。

表6: MATLABにおける演算結果との誤差

また、図23より、この回路の入力に対して出力が行われるまでのLatencyは3であることが得られる。